| Sensors                               | Data<br>Acquisition                  | Memory            | Processor                         | Output                | Actuators          |

|---------------------------------------|--------------------------------------|-------------------|-----------------------------------|-----------------------|--------------------|

| Voltage,<br>Current                   | A/D                                  | RAM               | Micro-<br>processor               | D/A                   | Loud-<br>speaker   |

| Temp-<br>erature                      | Codec                                | Dual Port<br>RAM  | Micro-<br>controller              | Digital               | Relay, Led<br>Lamp |

| Light,<br>Pressure,<br>Noise          | Digital<br>(Fifo, Latch<br>Register) | Multi Port<br>RAM | DSP                               | Display               | Switch             |

| Audio,<br>Ultrasound                  |                                      | Shared<br>RAM     | Transputer                        | SSI/SPI               | Motor              |

| Position,<br>Velocity<br>Acceleration |                                      | Fifo              | Gate-Array<br>Core-<br>Processor  | CAN,<br>Profibus      |                    |

| Human<br>Interfaces                   |                                      | FPGA              | DSP Multi-<br>Processor<br>System | Network<br>(Ethernet) |                    |

|                                       |                                      |                   |                                   | Bus-<br>Interfaces    |                    |

A more generall view to different functional blocks used in embedded systems.

### Interface techniques for data acquisition and control

### for MCU/DSP-based Embedded Sytsems

- MCUs provide high performance in general applications

- optimised for control flow applications with I/O-signals, complex interrupt interactions and user interfaces

- DSPs provide unbeatable performance in signal-processing applications by high computation power

- Optimised for high data transfers

- Single-cycle execution of fundamental processing operations by ALU, MAC and SHIFTER

- Intensive use of Multi-Instructions (single/multiple execute, fetch and store in one cycle)

- However lots of secondary processes/tasks have to be executed

- Data have to be acquired and/or output

- Signal processing is controlled by additional conditions from the environment and user settings (communication with a master processor, user interfaces, sensors and actuators)

- The benchmark examples of the manufacturers give us the impression, that the optimised code for the used algorithm is the whole work !

- For example: The code of a FFT algorithm assumes that the data are already available in the internal memory and often all internal busses are occupied by the optimised use of data movements.

- First the data has to be transfered from a source to the internal/external memory

#### Interface techniques for data acquisition and control

### for DSP-based Embedded Sytsems

#### • This is not realistic

- In parallel with the execution of algorithms, the processor has:

- To read from A/D-converters

- To write to D/A-converters

- store/read data samples in buffers

- sample I/O-ports

- communicate (read/write) with host MCUs or communication devices

- This different tasks often lead to interrupts, bus locks or bus collisions from internal to external memory.

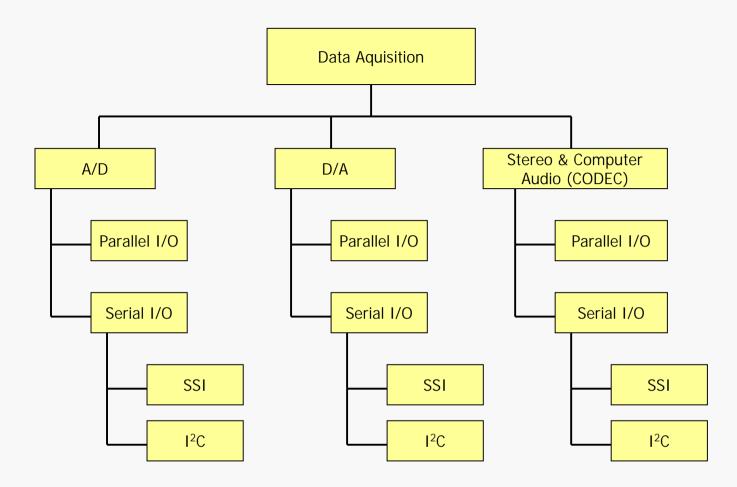

- Data Aquisition and data output

- Control Interface

- DSP and Memory

- Multiprocessing Techniques

- Code Development (Compiler/Linker)

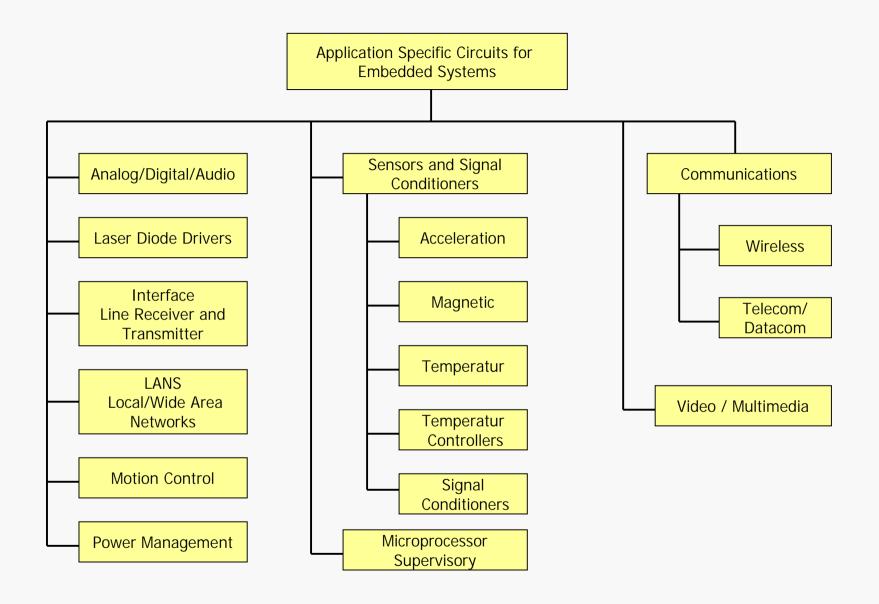

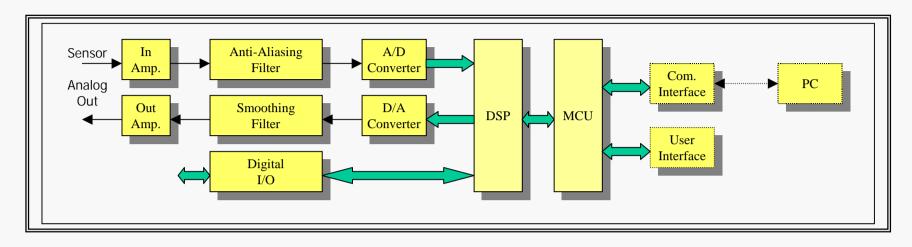

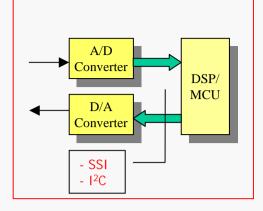

### Typical structure of Embedded Systems

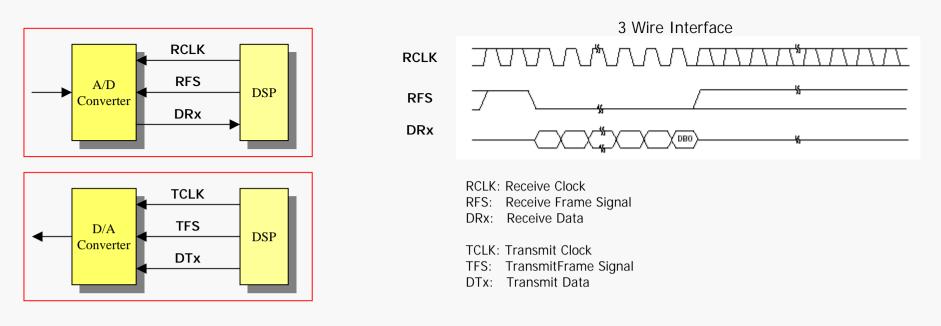

### Data Acquisition : Serial Interface

- Most DSP systems processes real-world-data

- by the aid of A/D and D/A converter

- digital data transmitted by point-to-point links or networks

- Aquisition of a data stream by a general synchronous serial interface (SSI or I<sup>2</sup>C)

- All general purpose DSP have at least one serial port built in peripheral

#### Advantages:

- Industrie standard converters and Codecs can be connected without additional glue logic

- Offer multi-channel-support for time division multiplex interfaces

- Easy to isolate and to decouple in electrically point of view

- Few signals (6) are necessary for bidirectional, independant data transfer

- Independence from external bus operations, SSI is able to work standalone

- Different techniques for data aquisition are possible

- Single write/read transfer

- DMA weite/read block-buffer transfer

- Polling mode

- Interrupt driven transfer

#### Disadvantage:

Slow data aquisition performance (typcially up to 200 KHz analog bandwith (max. 1 MHz)

- The mode of the SSI port can be configured by control registers

- Polarity of Frame signals

- Frame sync type

- Clock timing and frame cycle timing (internal or external)

- Multi-channel support for time division multiplex interface; pre-selected time-slots will be read to reduce transfer time and to releave the Core Processor

- Clocks and frame signals are generated internally: DSP is master

- Clock and frame signal are generated externally: DSP is slave

- The max. clock frequency is today 30 MHz up to 100 MHz (30 Mbit/sec to 100 Mbit/sec)

- The limitation is not the clock frequency; it is the analog bandwidth and the serializer of the A/D or D/A converter

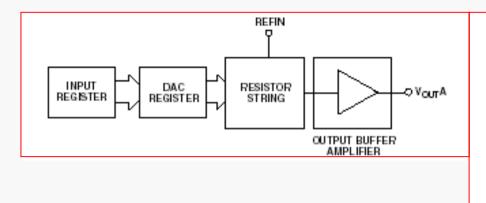

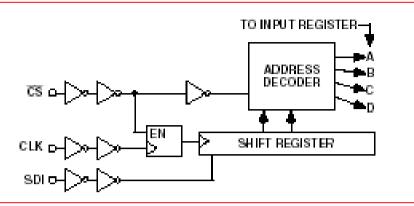

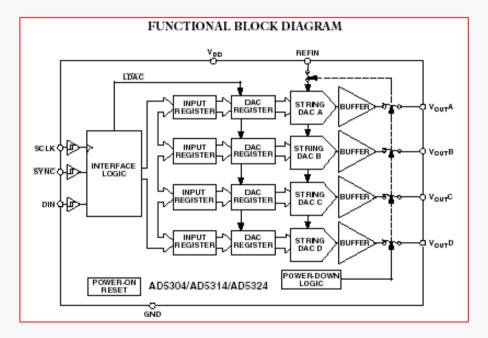

#### Example: AD5324 / Analog-Devices

- Quad Serial-Input D/A converter

- No additional Glue-Logic

- Four buffered 12-Bit DACs

- DSP-Compatible 3-Wire Serial Interface (SSI)

- Low Power, SPI, QSPI and Microwire Interface

- Additional Update Signal for all DACs

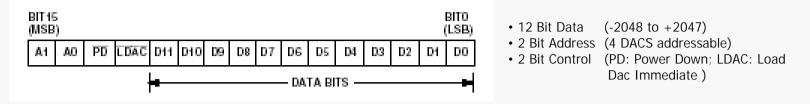

### Data Format for a 4 Channel DAC:

- Additional cycles are necessary to encode the data to the DAC

- Address selection

- Update Mode

- Power Down Mode

- Data tansfer from the converter to the memory is possible by

- Write/read by Core-Processor

- Polling mode

- Interrupt mode

- Not preferable, because the Core-Processor is locked by serial read/write for other tasks

- DMA mode (Direct Memory Address)

- Polling mode

- Interrupt mode

- Usefull for block buffer transfer

- Core-Processor is relieved for other tasks

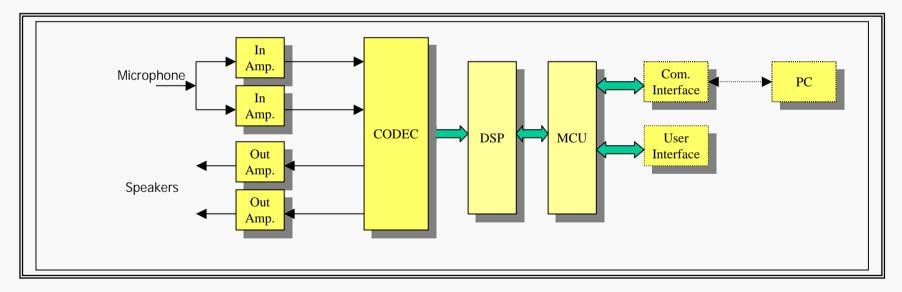

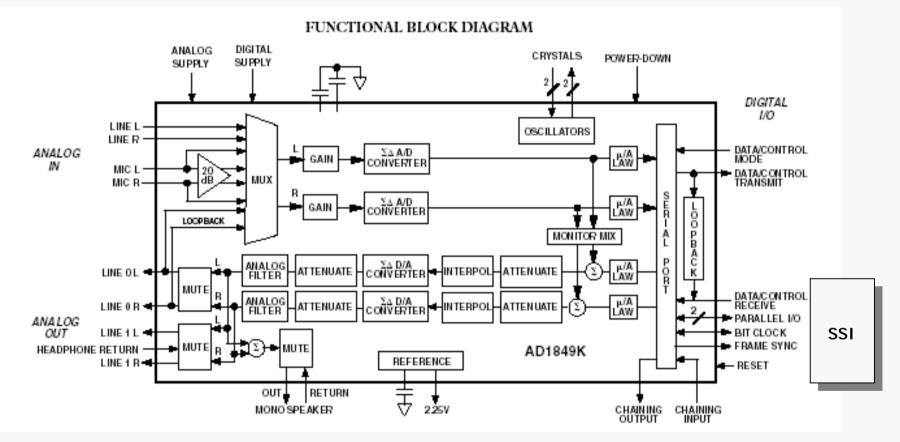

#### Special serial device for audio applications: Sound-Port-Codec

• Example AD1849 / Analog Devices

#### **General Description**

- The Serial-Port 16-Bit Stereo Codec integrates the audio data conversion and control functions in one single integrated device.

- A Codec is a single-chip audio solution for multimedia applications.

- Externel signal components and requirements are limited to three capacitors for line level application.

- So called Anti-Imaging filters are incorporated on-chip.

- The chip includes on-chip monoaural speaker and stereo headphone drive circuits.

- The dynamic range exceeds 80 dB across the audio bandwidth of 20 KHz.

- Sample rates up to 48 KHz are supported from external crystals, an external clock or from the serial clock of the SSI port.

- The Codec works with a pair (Stereo) of Sigma-Delta analog-to-digital converters and a pair of of Sigma-Delta digital-to-analog converters.

- Analog signal are fed to the chip at line levels or microphone levels.

- A programmable gain stage allows the setting of independant gains into the ADC

- The ADCs digital output data can be mixed with the DACs input.

- The channels (with 16-bit data) are available over a single bidirectional serial interface that also manages 16-bit digital input to the DAC and additional control information.

- Additional feature: compress and decompress technique.

- Integration of a digital interpolation filter and a attenuator control circuit for volume adaption.

- Nyquist images and quantization noise are removed from the DACs analog stereo output by an on-chip switchedcapacitor and continues-time filters.

#### Time and Frequency Considerations of SSI based Converters

| Serial     |               |               |  |  |  |

|------------|---------------|---------------|--|--|--|

| Interface  |               |               |  |  |  |

| Cycle time | Transfer rate | Transfer time |  |  |  |

| [us]       | [Mbit/sec]    | 16 Bit [us]   |  |  |  |

| 1          | 1             | 16            |  |  |  |

| 0.1        | 10            | 1,6           |  |  |  |

| 0.05       | 20            | 0,8           |  |  |  |

| 0.03       | 33            | 0,48          |  |  |  |

|            | Processor    | Analog<br>Signal |

|------------|--------------|------------------|

| Cycle time | Count of     | Frequency        |

| [ns]       | Instructions |                  |

| 0.025      | 640          | < 32 kHz         |

| 0.025      | 64           | < 312 kHz        |

| 0.025      | 32           | < 625 kHz        |

| 0.025      | 19           | < 1 MHz          |

Result:

- Use the highest possible data rate on SSI interface

- Use DMA transfer to releave the processor

- Use interrupt technology for event triggering

- •Typicall situation for audio processing

- 48 kHz sample rate

- 20.8 us / sample

- 20.8 us = interrupt

- 40 MHz DSP <-> at least 832 single instructions

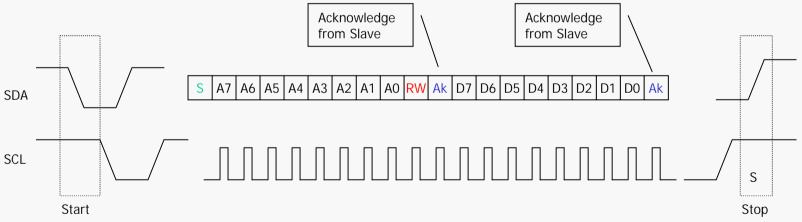

# I<sup>2</sup>C Interface

- I<sup>2</sup>C is a two wire interface with a special protocoll

- Used for slow A/D-, D/A converters and digital input/output devices (100 kHz)

- Uses a serial data I/O line (SDA) and a serial clock (SCL).

- A select line (as Frame) is not required

- Data transfer may be initiated only when the bus is not busy (multiple devices are possible)

- Each device has a unique address on the bus

- During such transfer, the data line (SDA) must remian stable whenever the clock line (SCL) is high

- Changes in the data line while the clock line is high are interpreted as a START or STOP condition

### I<sup>2</sup>C Interface

- A communication is set up by a master sending a start condition, a high-to-low transition on SDA while the serial clock (SCL) input is high

- After the start condition, the device address byte is send; MSB first, including the data direction bit (R/W)

- After receiving the valid address byte, the slave device responds with an acknowledge, a low on SDA during the high of the acknowledge-related clock pulse.

- The data bytes follows the address acknowledge. If the R/W bit is high a read cycle is performed.

- The data byte is followed by an acknowledge sentd from the device.

- Other data bytes are possible always followed by an acknowledge send from the device

- A stop condition, a low-to-high transition on the SDA input/output while the SCL is high, is send by the master after transfer

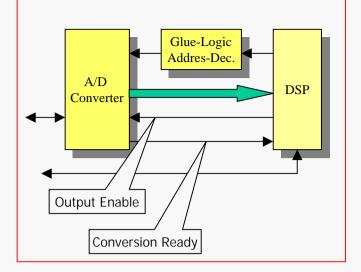

### Data Acquisition : Parallel Interface

- High-speed data acquisition usual requires a parallel interface because of the speed limitation of a serialized process.

- Aquisition of a data stream by a parallel interface

- All general purpose DSP have at least one parallel port, the external high-speed memory interface

- Different techniques for data aquisition are possible

- Single write/read transfer

- DMA write/read block-buffer transfer

- Polling mode

- Interrupt driven transfer

- Transfer via additional components (Fifo, Dual-Port-Ram, ...)

#### Advantages:

٠

High speed data aquisition

#### Disadvantages:

- Additional Glue-Logic

- Performance is dependent from external bus operations as memory accesses or othe DMA processes

- Alignment of the data bits of the converter to the bits of the processor format is necessary.

# Data rate by the different acquisition modes and transfer techniques

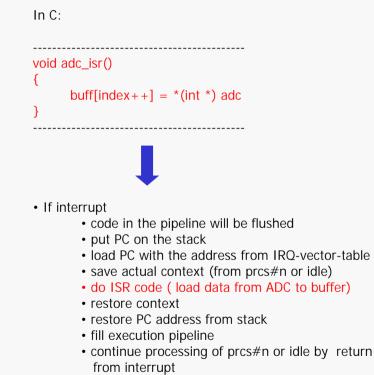

An ADC (parallel/serial) and an interrupt service routine (ISR) is used for data convert/transfer to an internal buffer; no additional buffering (Fifo,...) for the parallel mode is used

Result:

٠

We need a lot of additional cycles for reading one data

from the ADC

• Only continuous acquisition mode with low speed is possible

#### Problems

- Cycle time is not the only criterion; length of pipeline is important

- if external memory is accessed the time will increase (additional fetch cycles; in general only one external hardware bus interface is available, speed of external memory !

- C-Compilers will not always track the register usage inside the ISR and therefore will save and/or restore a partial set of registers, which wasts additional cycles)

- The interrupt implementation varies in C; (SHARC: needs 26 cycles (cycle-time: 25 ns) in the fastest mode (= 650 ns !)

- Solution: fast context switch to the second register/Index set and hand coded ISR entrance !

- It is not preferable to call a function inside the ISR

- If possible, the ISR should only set a flag; a dispatcher should manage the following actions by a normal function call

- Some instructions are not interruptable

- Interrupt nesting has to be used very carefully

#### Conclusion:

- Interrupt driven data transfer is not preferable above one or two MHz (depends on the processor)

- Use interrupt with the highest priority and enable the nesting mode

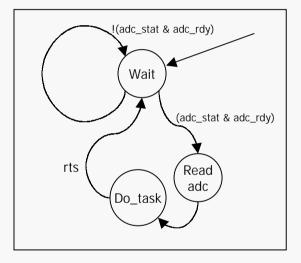

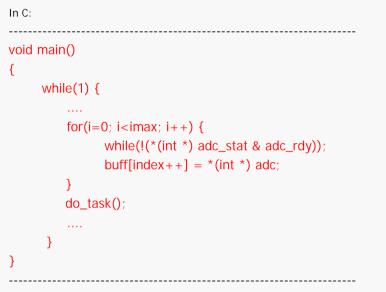

# Polling Mode

- An ADC (parallel/serial) and polling mode is used for data convert/transfer to an internal buffer; no additional buffering (Fifo,...) for the parallel mode is used

- The ADC ready signal is sampled by the processor-core

Result:

- We need fewer cycles as for the interrupt ISR

- If the DSP has BIT-Test fuctions or is able to test directly an I/O-signal, the process is much faster, but generally it demands hand coded inline assembly statements !

#### In C: void main() { while(1) { while(!(\*(int \*) adc\_stat & adc\_rdy)); buff[index++] = \*(int \*) adc;do\_task(); If interrupt • Loop1: load address register with adc\_stat to register load constant adc\_rdy to register Loop2: · load adc\_stat to register • perform .&' • if result = 0 jump Loop2 • load address register with adc • load address register buffer load register with index · load data from adc to register store register to buffer • increment index • perform the function ,do\_task' • jump Loop1

### Block-wise Polling Mode

- Polling mode has more efficiency if the dataacquisition is performed block-wise. In this transfer mode, the indices and addresses remain in registers. No re-load is required for each loop.

- In this case the data acquisition is non-continuous; no data are loaded during a signal processing task.

Best result, because we stay inside the loop, no re-load of register and addresses.

#### Conclusion

- Polling is only useful for block-wise and non-continuous data acquisition at high sample rate.

- For high speed applications interrupts or bus locking processes have to be prevent during polling mode.

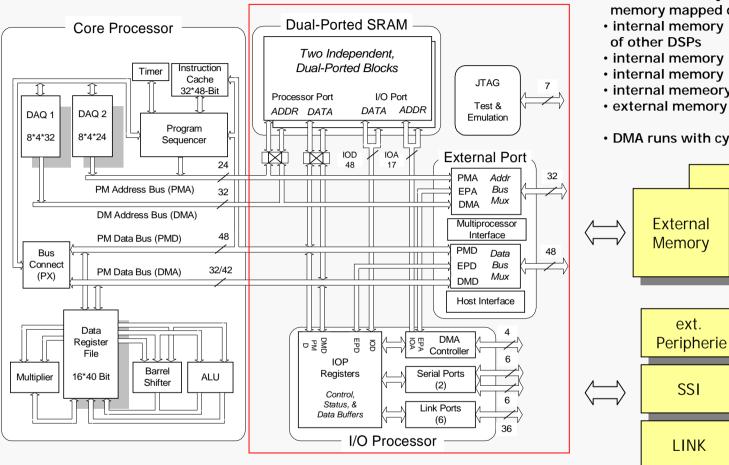

## DMA Transfer

- Nearly all MCUs and DSPs have efficient DMA controller capabilities without CORE access in order to move:

- data to and from memory

- data to and from built in peripheral

- The DMA process is event driven by an external DMA-request signal or by an internal start condition via watching status-register contents (serial transmitter/receiver buffer empty, full, .....).

- DMA controller increments automatically addresses or manages circular buffering.

- •

- Because the processor-core is not loaded with the action, the acquisition speed depends only from the maximum serial bit rate or the parallel transfer rate via the external bus.

- The process has to be synchronised to the data stream by watching DMA status bits or DMA complete interrupts.

- Best result are given by block-mode transfer (input to buffer, buffer to output, internal buffer transfer)

- DMA data transfer may be continuous too (depends from the application)

#### **Example SHARC DSP**

DMA process:

- internal memory <-> ext. memory and memory mapped devices

- internal memory <-> internal memory

- internal memory <-> host processor

- internal memory <-> serial port I/O

- internal memeory <-> link port I/O

- external memory <-> external peripherie

- DMA runs with cycle steeling from the core

Device

#### **Examples: DMA Transfer**

#### In C:

```

#defineDMA_src0xe1#defineDMA_dst0xe2#defineDMA_src_inc0x3e#defineDMA_dst_inc0xe4#defineDMA_count0xe5#defineDMA_start0x3252

```

volatile int src\_buf, dst\_buf, src\_inc, dst\_inc, cnt;

```

void main()

```

{

```

while(1) {

DMA src = src buf[0];

/* initialize DMA */

DMA_dst = dst_buf[0];

/* .. */

DMA src inc = 1;

/* .. */

/* .. */

DMA dst inc = 1;

DMA\_count = 1024;

/* .. */

DMA start = START;

/* start DMA */

while(!dma_ready);

/* polling mode: wait on DMA

ready */

do_signal_process();

IDLE:

```

#### Result:

- The speed depends on the data rate of the used transfer ports (serial, parallel).

- A DSP with 25 ns bus cycle is able to transfer 40 data values per microsecond (40 Mbyte/sec) if internal memory is used and there are no collisions with other DMA processes.

- The process has to be carefully tested for bus idle cycles and possible bus conflicts, in order to determine the achievable maximum speed.

Whereever applicable use a DMA process, because DMA save core-processing time.

#### Speed-up of data acquisition

- If the acquisition speed is above 20 MHz, the DSP needs additional hardware assistance to perform the required specification.

- Different techniques exists:

If the data-aquisition has a finite count of samples:

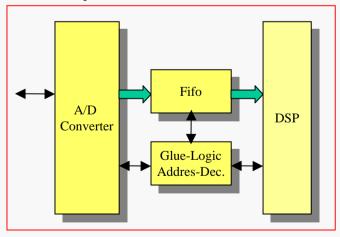

- Integration of a fifo structure for block-read operations.

- Bank switching techniques (Ping-Pong, ...).

- Fit the bit-size of external devices carefully to the bit-size of the processor to save processing time; connect the external bits to the upper data bits. Additional masking and shifter operations depends on the selected processor.

The data-aquisition process is always active and/or faster than the clock cycle:

- Data preprocessing by high speed Gate-Array based devices, e.g. to reduce the sampling frequency (sampling rate) before the data are passed to the processor for further processing steps.

- Use Multiprocessing Systems, More in the Lecture about Signal Processing Techniques

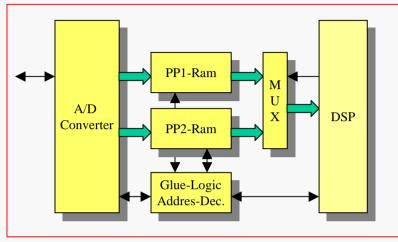

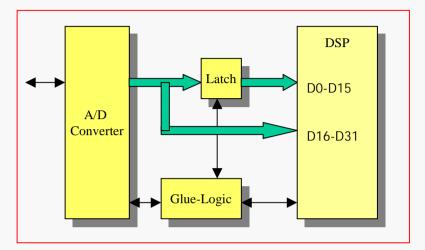

### Speed-up of data acquisition by additional buffering

Ping-Pong Memory (PP)

Fifo memory

# SHARC-code examples in Assembler for transfer of data via serial interface

#### Assembler for SHARC : Single Word without • Interrupt (by Core-Processor)

```

#include <asm_sprt.h>;

#define N 8

.SEGMENT /pm seg_pmco;

.global

_SerTransfer;

.extern

rbuf:

SerTransfer:

entry;

/* save data register & address register */

puts=r0;

r0=i0; puts=r0;

r0=b0: puts=r0:

r0=l0; puts=r0;

r0 = 0x00130007;

/* definitions for serial transfer */

dm(TDIV0)=r0;

/* load to ser CLOCK register */

r0 = 0x000064f1;

/* definitions for serial transfer division */

dm(STCTL0)=r0;

/* load to ser CONTROL register */

b0=rbuf:

/* pointer to rbuf[0] */

/* length of rbuf */

10=@rbuf:

lcntr=N, do tx_loop until ce;

/* if TXO is nit empty, Core-processor halts !! */

r0 = dm(i0,1);

tx\_loop: dm(tx0)=r0;

r0=gets(1); l0=r0;

/* restore data register & address register */

r0=gets(2); b0=r0;

r0=gets(3); i0=r0;

r0=qets(4);

alter(4);

exit;

.endseg;

```

#### Assembler for SHARC : Single Word with . Interrupt

```

#include <asm sprt.h>;

#define N 8

.SEGMENT /pm seg pmco;

_SerTransfer;

.global

.extern

rbuf:

SerTransfer:

entry;

```

#### /\* save the used register on stack !! \*/

```

r0 = 0x00130007;

dm(TDIV0)=r0;

r0 = 0x000064f1:

dm(STCTL0)=r0;

b0=rbuf;

10=@rbuf

bit set mask imask SPT01:

bit set mode1 IRPTEN;

r0=dm(i0,1);

dm(TX0)=r0;

```

/\* definitions for serial transfer \*/ /\* load to ser CLOCK register \*/ /\* definitions for serial transfer division \*/ /\* load to ser CONTROL register \*/ /\* pointer to rbuf[0] \*/ /\* length of rbuf \*/ /\* enable sport0 interrupt \*/ /\* global IRQ enable \*/

/\* kick off sport0 \*/

```

/* restore the register from stack */

exit:

Serial Interrupt works as a background task------

s0tx: rti(db);

r0=dm(i0,1);

dm(TX0)=r0;

```

```

.endseg

```

| Assembler for SHARC : DMA Transfer with Interrupt                                                                            |                                                                   |                                                                                                                                                                                |  |  |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <pre>#include <asm_s #define="" 64="" entry;="" externalserdmatransfer="" n="" pre="" save="" the="" used<=""></asm_s></pre> | :<br>register !!                                                  |                                                                                                                                                                                |  |  |

| r0=dbuf;                                                                                                                     | dm(II1)=r0;<br>dm(IM3)=r0;                                        | /* start pointer of source buffer */<br>/* start pointer of destination buffer */<br>/* DMA increment */<br>/* DMA increment */                                                |  |  |

| r0=0x0013000                                                                                                                 | dm(C3)=r0;<br>dm(C1)=r0;<br>1; dm(SRCTL1)=r0;<br>7; dm(TDIV1)=r0; | <pre>/* lenght of source buffer */ /* = length of destination buffer */ /* set serial control register 0 */ /* set clock register */ /* set serial control register 1 */</pre> |  |  |

| bit set imask SPRLI;<br>bit set mode1 IRPTEN;<br>restore the used register !!<br>exit;                                       |                                                                   | /* enable sport1 receive interrrupt */<br>/* global IRQ enable */                                                                                                              |  |  |

| s1rx: rti;<br>.endseg;                                                                                                       |                                                                   | /* this interrupt will occur only once */                                                                                                                                      |  |  |

#### Assembler for SHARC : DMA

- This example shows the use of on-chip DMA controller to handle serial data. The controller realizes data transfers between internal memory and the SPORTs, providing the most efficient way of block-mode-transfer. When the DMA is set up, the DMA controller operates independently from the SHARC processor-core. The interrupt is only active for one time when an entire data-block has been received (or transmitted). This frees the core to continue other tasks.

- This example sets up a SPORT DMA transfer and receive for serial SPORT1 in the loopback mode, The buffer sbuf is transfered by DMA out of the SPORT. The loopback mode internally attaches the different control signals. The receive DMA places the data in the buffer dbuf.

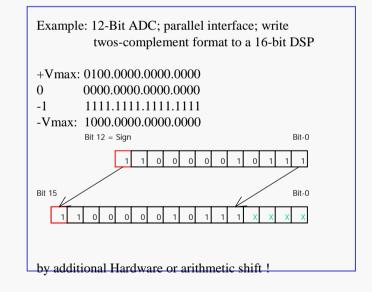

# SHARC-code examples in C and Assembler for transfer of data from a fifo to internal buffer

The 16 bit of the Fio are connected to D31-D16:

• needs a arithmetic shift for 2er complement

```

Assembler for SHARC without multfunction

Assembler with multifunction instructions

٠

• Copy a buffer from Fifo to memory

instructions

•

Copy a buffer from Fifo to memory

٠

#include <asm sprt.h>:

.SEGMENT /pm seq_pmco;

.global

ASMFast:

#include <asm sprt.h>;

rbuf:

.extern

.SEGMENT /pm seg_pmco;

.extern

TsCnt:

ASMFast:

ASMCpyExtFifoToMem;

.global

.extern

rbuf;

entry;

TsCnt:

.extern

_ASMCpyExtFifoToMem:

puts=r0;

entry;

puts=r2:

puts=r4:

puts=r0;

/* save data register & address register */

r0=i1; puts=r0;

puts=r2;

r0=i4; puts=r0;

r0=i1; puts=r0;

r0=i4: puts=r0:

i4 = 0x440004

/* fifo base address */

i4=0x440004:

i1 = rbuf;

/* pointer to destination buffer[0] */

r0=dm(_TsCnt);

i1 = rbuf;

/* destination buffer */

r0=ashift r0 by 0xfffffff;

/* TsCnt / 2 */

r0=dm(_TsCnt);

r2=dm(i4,m5);

/* rbuf[0] */

Icntr=r0, DO loop1 UNTIL LCE; /* (N * 3)*cycle time */

/* load from fifo, m5 = 0 */

r2=dm(i4,m5);

Icntr=r0, DO loop3 UNTIL LCE;

r2=ashift r2 by 0xffffff0, r4=dm(i4,m5);

r2=ashift r2 by 0xffffff0;

/* alignment of 16 bit to 32 bit bus */

r4=ashift r4 by 0xffffff0, dm(i1,m6)=r2:

loop1: dm(i1,m6)=r2;

/* store ti internal buffer */

r_2=dm(i4.m_5)

loop3: dm(i1,m6)=r4;

/* restore data register & address register */

r0=gets(1); i4=r0;

r0=gets(2); i1=r0;

r0=gets(1); i4=r0;

r2=qets(3);

r0=gets(2); i1=r0;

r0=gets(4);

r4=gets(3)

(1024 * 3) + 17 = 3089

alter(4);

r2=qets(4)

exit:

r0=gets(5);

.endseg;

alter(5);

exit;

```

(512 \* 4) + 20 = 2068

.endseg;

| Assembler for SHARC without multifunction     instructions and modulus                                                                                                                                                                                                                                                                                                 | Assembler for SHARC with multifunction     instructions and modulus function                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>#include <asm_sprt.h>;SEGMENT /pm seg_pmco; .globalASMCpyExtAbsFifoToMem; .externrbuf; .externTsCnt; _ASMCpyExtAbsFifoToMem:     entry;         puts=r0;         puts=r2;     r0=i1; puts=r0;     r0=i4; puts=r0;     i4=0x440004;     i1=_rbuf;     r0=dm(_TsCnt);     Icntr=r0, DO loop2 UNTIL LCE;         r2=dm(i4,m5);         r2=abs r2;</asm_sprt.h></pre> | <pre>SEGMENT /pm seg_pmco;<br/>.global _ASMFastAbs;<br/>.extern _rbuf;<br/>.extern _TsCnt;<br/>_ASMFastAbs:<br/>entry;<br/>puts=r0;<br/>puts=r2;<br/>puts=r4;<br/>r0=i1; puts=r0;<br/>r0=i4; puts=r0;<br/>i1=_rbuf;<br/>r0=dm(_TsCnt);<br/>r0=ashift r0 by 0xfffffff;<br/>r2=dm(i4,m5);</pre> |

| (1024 * 4) + 17 = 4117                                                                                                                                                                                                                                                                                                                                                 | .endseg; $(512 * 4) + 20 = 2068$                                                                                                                                                                                                                                                              |

#### Data Output

The results of the tasks may be output via D/A converters, transfered to other systems for further processing or visualization, controls actuators via I/O-ports, field buses, networking components etc... For D/A-converters, we use the same techniques and have the same restrictions.

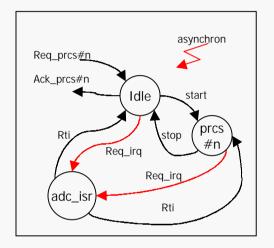

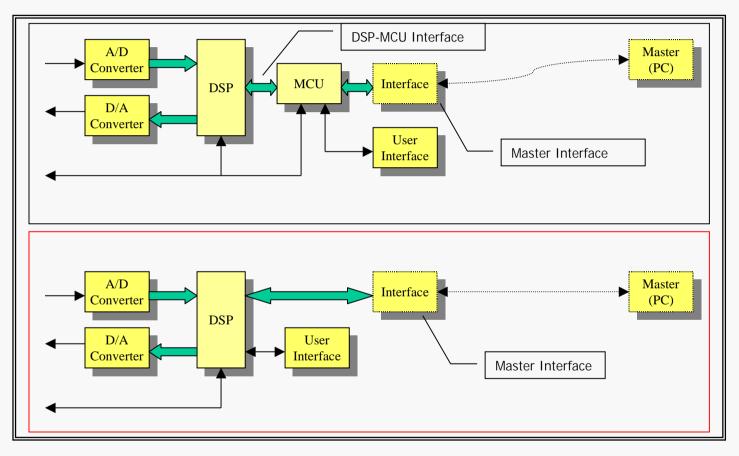

## Control Interface Technology

- Not all DSPs/MCUs can operate without external control devices.

- Most systems require additional devices (MCUs) for result-data transfer, visualisation and user interface capabilities.

Solutions:

- Direct connection of keypads and displays to the DSP

- Direct bus interface by a micro-controller or a Master-system (Isa-Interface, PCI-Interface)

- Usage of bidrectional serial ports to conect to a HOST

- Integration of serial and parallel interfaces as RS232, RS422, RS485

- Integration of networks (Ethernet, Can, USB, Profibus)

- The choice depends on the overall application and the given requirements

## Control Interface Technology

Typical structure of Embedded Systems

## Control Interface Technology

- DSP to MCU (Master) by the built in parallel Host interface

- Host interface uses its own address, data and control siognals (independent)

- The host will take the control over the DSP via bus arbitration logic

- problems if the host is slow, the host locks the performance of the DSP

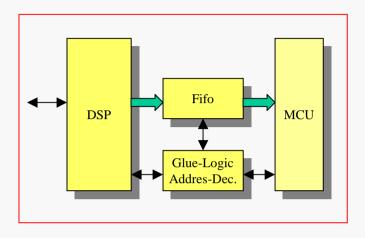

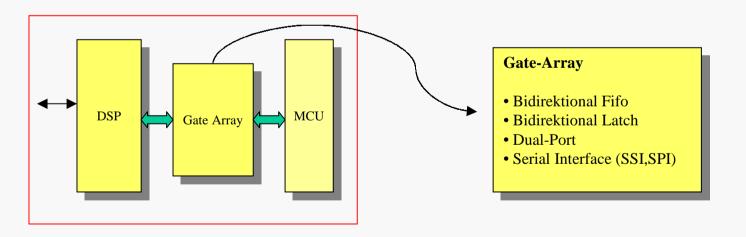

- Bidirectional register or latches with interrupt signals

- Bidrectional fifo structure with additional GLUE logic (in a Gate Array !)

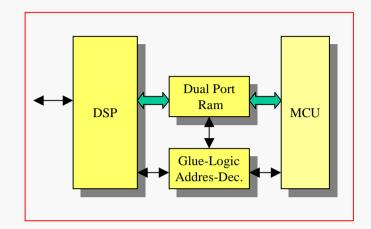

- Dual-Port-Memory with interrupt signals

- Serial interfaces as SSI, SPI (fits in a CPLD or a small Gate Array)

Best choice if the data transfer is decoupled !

We need a protocol !

#### Host Interface Technology

- Multprocessing

- Industrial Interfaces

- Network and Protocol